Mirabilis Design Inc.

Suite 116

Sunnyvale, CA 94087 [email protected]

408-245-8992

https://www.mirabilisdesign.com/

Mirabilis Design’s SEAL Teaches Tech Innovations to Everyone - News

January 16, 2023Santa Clara, CA and Chennai, India. Mirabilis Design Inc, revealed its Semiconductor and Embedded Systems Architecture Labs (SEAL). SEAL is designed as a learning platform for anyone interested in strengthening their theoretical and software competences with hands-on and visualization learning. It supports curriculum integration with a combination of trusted content on standards and applications such as VisualSim Cloud Graphical Simulation Platform, brain storming questions, and answer keys.

Embedded World 2022 Best in Show Winners: Development Tools & Operating Systems - Story

June 17, 2022Winners have been chosen based on a 15-point rubric that considers solutions’ Design Excellence (5 points), Relative Performance (5 points), and Market Impact/Disruption (5 points).

Mirabilis Design VisualSim Antenna Designers - Product

June 16, 2022VisualSim Antenna Designer is a datasheet-driven antenna simulation platform for communication system feasibility, evaluate antenna response to real-life scenarios and compare antennas for an application.

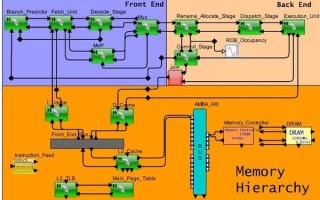

Hybrid Innovations for Processor Architecture Exploration - Story

July 20, 2021Architecture exploration has been the holy grail of product design. It has the potential to completely transform product engineering. Research and use cases evaluations have shown that 80% of system optimization and almost 100% of the performance/power trade-offs can be achieved during architecture exploration.

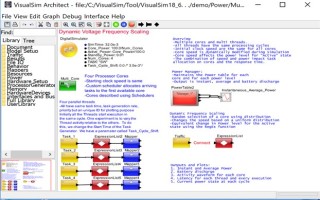

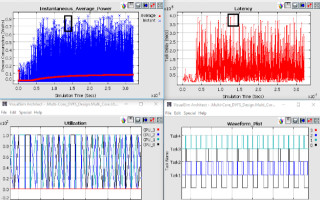

Power Modeling and Estimation in Early System Design, Part 2 - Story

June 28, 2021In Part 1 of this two-part series we addressed the need for early-stage power analysis in complex SoCs and system designs, and introduced the VisualSim graphical modeling tool as a comprehensive energy simulation solution. In Part 2, we show how VisualSim performs when forecasting and expressing power values across several scenarios (offset concurrent tasks; comparing a single core at 1 GHz to four cores at 250 MHz; dynamic voltage frequency scaling (DVFS); and power gating) in a multicore embedded environment.

Power Modeling and Estimation in Early System Design, Part 1 - Story

June 28, 2021With the increase in SoC design complexity, system-level power estimation is becoming a critical factor. Part one of this two-part series explains why this is the case and introduces a comprehensive modeling platform for evaluating the power consumption of subsystems, chips, and entire systems.

IBM's 2 nm Transistor Breakthrough Puts Chip Design Under the Microscope - Story

June 18, 2021The company claims that its 2 nm research chip’s “tiniest components are smaller than a strand of DNA.”