Power Modeling and Estimation in Early System Design, Part 1

June 28, 2021

Story

With the increase in SoC design complexity, system-level power estimation is becoming a critical factor. Part one of this two-part series explains why this is the case and introduces a comprehensive modeling platform for evaluating the power consumption of subsystems, chips, and entire systems.

As application scalability increases, low power consumption has become as important as processing performance in many cases. Until now, unfortunately, design engineers have used spreadsheets to estimate system-level power consumption.

This approach is very time consuming and error prone, especially when working with complex SoCs and sophisticated power management techniques. Power analysis must be performed at each abstraction level with a high degree of accuracy in order to achieve confidence in a design's power consumption and the effects of power optimization.

For example, determining the overall energy profile of an architecture requires analysis that ranges from power consumption to energy management, as well aas how these factors interact with mechanical enclosures. Early feedback is required in order to understand the limitations and requirements of the system, and how the scalability of system impacts power is a major factor in the future of your system.

Throughput analysis is not sufficient. It is necessary to understand power at very early stages of design.

Comprehensive Modeling for Power Measurement

VisualSim presents a new methodology that provides early-stage power estimation, enabling designers to quickly evaluate the energy profile of different architectures and power management techniques through a graphical modeling environment. VisualSim is a model-based system simulation software that accelerates development using a component-based modeling methodology and offers a large portfolio of reports. The system can be a processor, SoC, autonomous driving assistance system, flight avionics controller, or adventure camera. The modeling components can be a resource, FPGA, discrete component, electrical system, MEMS, processor, distribution-based traffic generator, hardware peripheral, or software graph. With VisualSim, one can analyze and model power generation, storage, consumption, and management, as well as its impact on the system, subsystem, and chip level.

Specifically for the purposes of this article, the VisualSim Power Modeling Toolkit provides a system-level power exploration solution that captures the generation, storage, and consumption of energy in a system or semiconductor. It can even calculate dynamic power by capturing the state changes of a device.

The hierarchical power analysis permits power modeling from the chip level to a network of IoT systems via three unique power-modeling blocks.

- Energy Harvester Block:

- Provides a convenient way to emulate motor-based power harvesters

- Supports different time-based mechanisms like wind turbines, for example

- Can be directly connected to battery-charged devices

- Power Table:

- Studies and models the power infrastructure

- Determines power consumption from resource operations

- Supports the design of optimized power management algorithms

- Simplifies the selection of appropriate battery configurations for battery operated devices

- Power Manager Block:

- Communicates with each IP block with power functionality about its operational state

- Modules can be defined that provide custom power consumption statistics

- Supports a user-specifiable power-gating mechanism

- Can capture instantaneous power changes

VisualSim takes the activity of devices and state changes, like the logic for moving from sleep to deep sleep, into consideration. It also keeps track of power consumption in each of these states, different power levels for different tasks, and different power generation processes.

Power Generation & Battery Models

VisualSim provides variety of power generation blocks. VisualSim includes power data for a number of devices currently on the market, which saves users time and effort, but you can also input a trace of an existing system power profile and debug it within the platform.

Also included are a variety of battery models that go beyond the emulation of charge and discharge based on system requests. The battery models incorporate external shocks and thermal activity, number of charge/discharge cycles and their rate, and the number of power surges, as well as how all of these impact battery life and maximum charge.

These system architecture parameters can then be optimized using the VisualSim Power Table.

Power Table

The Power Table works in conjunction with battery and energy harvesters to measure experimental power management algorithms and their potential impact on power consumption. Like the rest of VisualSim, it can accomodate dynamic state changes, different state durations within a device, and works in conjunction with the timing of the model (although it does introduce a delay related to transition time between states).

Custom Blocks

The custom block can be a single instance with multiple states. Power states are changed using the power update RegEx.

Custom devices can also be a block with multiple identical instances within a single device. A good example of this is the Root Complex ports in PCIe. Here, the ports differ in the number of lanes and the power for different lane counts would be the custom state columns Active_4, Active_8, etc. where each port is a queue number.

As each port receives a request, it can be added to the Power Table queue as an instance of PCIe. This is done using the powerUpdateN RegEx operator.

Figure 1. Power Table configuration.

As you can see in Figure 1, the parameters of the power table blocks are divided into three main areas.

- Manager Set-Up maintains the list of following attributes:

- Device name: Maintains a list of all the device in the Power Table

- Power states: Lists and displays all the different types of states

- State transitions: Keeps track of active and inactive states based on the type of task that’s being threaded.

- Exist: Gives the current state of device.

- Async-State-Change contains a 'Time state" that displays the period of time before the state should change, which can be set as needed.

- Expression List allows designers to implement different logic about the power values and state changes. It also supports whatever the Expression List block's logic and RegEx are. The expression must be of single line and terminate with ';'.

Towards Real-World Power Profiling

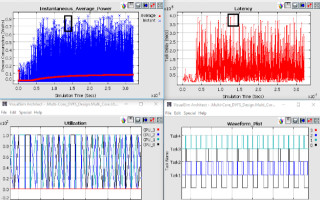

As discussed, the VisualSim modeling and simulation environment is equipped with all of the capabilities needed to accurately determine the power profile of systems ranging from IP blocks to complex, multi-device deployments. To prove its worth in action, Part Two of Power Modeling and Estimation in Early System Design will demonstrate how the tool performed in several research scenarios, including:

- Offset concurrent tasks

- Comparing a single core running at 1 GHz versus four cores at 250 MHz

- Dynamic Voltage Frequency Scaling (DVFS)

- Power Gating

These scenarios are executed on a quad-core processor that uses a dispatcher to execute four concurrent threads and interrupts.