The Road to the RISC-V Summit: Microchip

October 30, 2023

Story

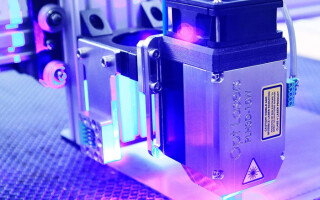

Microchip is packing up in Chandler, Arizona and will start its trip to the RISC-V Summit in Santa Clara, California, November 7th and 8th, 2023, and November 6 being Member Day. Microchip will be demonstrating its market leading FPGA solutions for the intelligent edge and how it leverages the RISC-V ISA to design heterogenous processing architectures for non-proprietary instruction set architectures.

Microchip’s utilization of RISC-V enables flexible caches, asymmetric processing on single application class clusters (bare metal development), real-time applications, and inferencing for AI/ML.

The platforms meet the needs of edge AI in applications including industrial, communications, medical, automotive, IoT, aviation, and defense. Microchip’s FPGA’s offer the flexibility, power, security, and thermal efficiency when presented with harsh environmental conditions.

The innovative software design tools include High Level Synthesis (HLS) for implementation of C/C++, Software Development Kits (SDKs) for vector-based processing (AI/ML inferencing), and solution stacks delivering industrial automation, and intelligent machine vision.

BeagleBoard will be in attendance highlighting its hardware and other solutions complementing Microchip’s extensive Mi-V Ecosystem.

Microchip at the RISC-V Summit:

- Microchip FPGA spokespeople will also be participating in several keynote and technical sessions including:

- Keynote: “100G Intelligent Edge innovations with RISC-V (the future is now),” presented by Bruce Weyer, Vice President, Microchip FPGA business unit, Nov. 7 at 9:55 a.m. in the Mission City Ballroom B2-B5.

- Technical Session: “Accelerating Designs for SoC FPGA Using Simplified High-Level Synthesis Flows,” presented by Manuel Saldana, Senior Technical Engineer, High-Level Synthesis, Microchip FPGA business unit, Nov. 8, 2:35 p.m., Theater.

- Member Day Session: “Future Direction of RISC-V Cryptography Extensions,” presented by Richard Newell, Associate Technical Fellow, Microchip, and Nicolas Brunie, Principle Engineer, SiFive, November 6, 1 p.m., Theater.

- Member Day Session – RISC-V 101 Ecosystem, presented by Ted Speers, Microchip Technical Fellow, Monday, November 6, 9 a.m.

For more information, visit: Microchip and the official RISC-V Summit page.