Applied Materials Introduces New Materials to Advance DRAM Technology

May 10, 2021

Blog

Memory technology doesn’t always advance at the swiftest pace, but there’s been some movement in this space as of late.

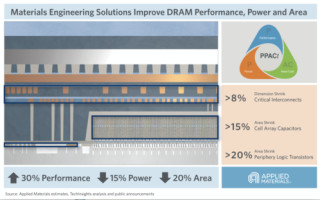

One example comes from Applied Materials, who announced a series of materials and engineering solutions designed to offer three new ways to scale DRAM products, while potentially accelerating improvements in chip performance, power, area, cost, and time to market. The target areas for these new products are in IoT and AI. This comes as “the industry urgently needs breakthroughs that can allow DRAM to scale and reduce area and cost while also operating at higher speeds and using less power,” according to Applied Materials.

The company is working with DRAM customers to commercialize three engineering solutions that create new ways to shrink as well as improve performance and power. The solutions target three areas of DRAM chips: storage capacitors, interconnect wiring, and logic transistors. All three technologies are now ramping into high volume production.

Because more than 55% of a DRAM chip’s die area is occupied by the memory arrays, increasing the density of these cells can have the largest impact on reducing the cost per bit. Data is stored as a charge in cylindrical, vertically arranged capacitors that need as much surface area as possible to hold an adequate number of electrons. As the capacitors narrow, they elongate for a maximum surface area. Applied Materials’ solution, dubbed Draco, provides a new hard mask material that’s optimized to work with the company’s Sym3 Y Etch system. The system is designed to increase etch selectivity by more than 30%, enabling a shorter mask.

A second strategy being deployed by Applied Materials is reducing the die area needed by the interconnect wiring that routes signals to and from the memory arrays. Each of the metal lines is surrounded by an insulating dielectric material to prevent interference between the data signals. Per the company, this eliminates the problem of thinning dielectric layers. The Black Diamond solution uses a low-k dielectric material that enables smaller, more compact interconnect wires that can move signals through the chips at multi-gigahertz speeds, without interference, and at lower power consumption.

The third advancement from Applied Materials is to improve the performance, power, area and cost of the transistors used in the chip’s periphery logic to help drive the I/O operations needed in high-performance DRAM. Previously, DRAM used transistors based on polysilicon-oxide that wasted power and limited performance. Today’s devices use a metal gate and a dielectric with hafnium oxide, a material that improves gate capacitance, leakage, and performance. That material is known as High-k metal gate, or HKMG.