FPGA-based prototyping revisited - Cadence Protium S1 Platform

March 13, 2017

The IoT spans multiple application domains and the requirements for design teams can be vastly different depending on the end application area. While...

The IoT spans multiple application domains and the requirements for design teams can be vastly different depending on the end application area. While power, performance, and cost are standard priorities to meet in silicon design for electronics components, application domains like automotive and aerospace/defense add safety to the lists of design priorities, while in others, security is key or in-field upgradability needs to be considered.

Verification, prototyping, and software development are common threads across these domains and design requirements. To allow embedded software development, classic early verification techniques like simulation are often considered too slow, while abstraction with virtual platforms like QEMU sometimes is considered not accurate enough.

FPGA-based prototyping has long been a preferred platform for pre-silicon software development. Compared to its big brother, hardware emulation, in tools like the Cadence Palladium Z1 Enterprise Emulation Platform, it scales to faster execution performance from the MHz level to 10s of MHz or even the 100-MHz range, and it also comes at a lower cost, allowing it to be replicated to more members of the software team.

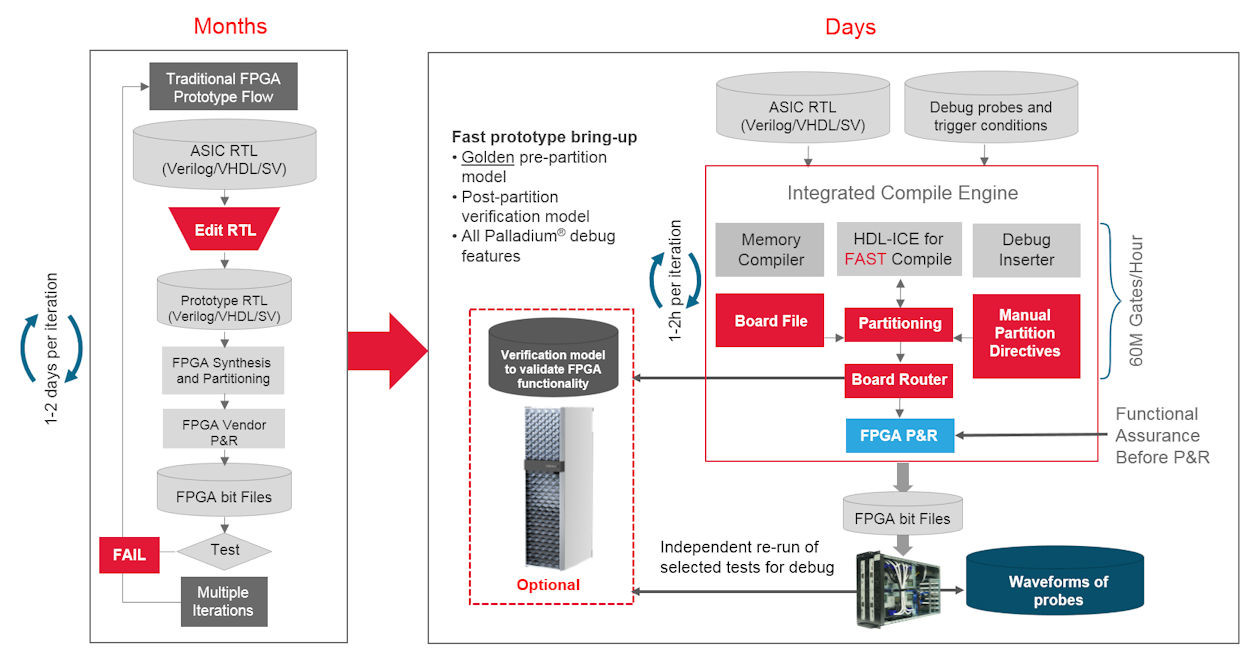

Traditionally, the hurdle for FPGA-based prototypes has been its bring-up process, sometimes resulting in months passing by before it can be made available for software developers. The reason has been the need to re-map the ASIC design from its actual silicon target technology into the fabric provided by FPGAs, requiring re-mapping of parts of the design.

For starters, memories in the ASIC need to be mapped into resources available in the FPGA, or into daughtercards holding specific additional memory like DDR. Dealing with the ASIC’s clocking can be a nightmare, with 10s of clocks to be synchronized in more complex designs on the PCB and the FPGA. Partitioning of the design across multiple FPGAs is far from trivial and often requires multiplexing multiple signals across the same pin using low-voltage differential signaling (LVDS) techniques.

[Cadence multi-fabric compile flow for Palladium Z1 and Protium S1 platforms.]

Bigger companies traditionally have had prototyping teams that specialize in taking a version of the RTL under development by the design team and mapping it into FPGAs. However, with rising design complexities, it’s become increasingly difficult to perform all the tasks described above while the software developers are hovering impatiently over the team to get access to it.

With the Protium S1 FPGA-Based Prototyping Platform, Cadence has re-visited prototyping and has focused specifically on reducing the time to prototype from months to weeks or even days. It has done so by enabling congruency between Palladium Z1 emulation and Protium S1 FPGA-based prototyping, re-using some of the emulation front-end for prototyping, as well.

Complex manual memory modeling has been automated using memory models known in emulation; the compile flow takes care of the partitioning between FPGAs and clock synchronization. Netlists that are to be mapped into FPGA fabrics can be validated in emulation, saving valuable place-and-route time. Once defects have been identified in FPGA-based prototyping at about 5X higher speed than emulation, the same design can be pushed back to emulation to utilize the much better debug capabilities available there.

As part of the Cadence Verification Suite that also includes formal verification, simulation and emulation, FPGA-based prototyping has just been re-invented using automation and made available to a much broader audience of developers for IoT designs. For more information, visit us at embedded world 2017 in Nuernberg at booth 4-116 in hall 4.