RISC-V: Too Open to Succeed

September 28, 2019

Blog

Earlier this year, I wrote a column entitled ?RISC-V: Too Open to Fail?. Now it?s time to look at a few reasons the technology could fail. And they start with the fact that RISC-V is open source.

Earlier this year, I wrote a column entitled “RISC-V: Too Open to Fail” in which I outlined several reasons why the open hardware initiative will be a success.

Now it’s time to look at a few reasons the technology could fail. And they start with the fact that RISC-V is open source.

Can open-source hardware really be a long-term commercial success?

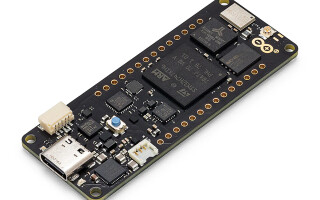

As a reminder, RISC-V defines an open-source, royalty-free instruction set architecture, not actual IP cores or chips. Cores based on the ISA are being developed by companies like Si-Five, Codasip, Esperanto, and GreenWaves. Even well-established industry players like Andes and Western Digital have RISC-V cores. NXP and Microchip (via its Microsemi acquisition) have SoCs based on RISC-V.

But there’s the rub: Because only the ISA is defined, core implementations can – and do – vary across vendors. In fact, Si-Five, the de facto RISC-V IP standard bearer, has publicly announced multiple engagements of customizing RISC-V cores for specific client use cases.

This flexibility to customize and tune the most fundamental hardware building blocks to the specific needs of a particular application is the beauty of open-source technology. This aspect is especially true at a time when we can no longer rely on physicists to provide higher performance, lower power, and reduced costs every 18 to 24 months.

But the flexibility of open-source hardware could also potentially be its downfall. It’s a matter of conformity and compliance, as currently there are no tried-and-true guarantees that a RISC-V core from one IP vendor can be used in place of another’s without significant rework down at the VHDL/Verilog level. And that can be incredibly expensive.

There is a RISC-V Compliance Task Group, but there hasn’t been much news out of it in several months. I expect there to be an update at this December’s RISC-V Summit in San Jose, but time will tell.

Without more strict compliance, betting a system design on a core from one of the many RISC-V startups, for example, can be a frightening proposition for customers. The looser environment also makes it more difficult for software ecosystems to take hold.

Without software?

Previous open hardware initiatives like OpenRISC and OpenSPARC failed commercially largely because no software ecosystem ever materialized around the relatively few cores that were produced. RISC-V has a similar problem, only in the sense that with the potential for so many different core permutations it will be difficult for tools, middleware, and operating system providers to develop and support a robust software ecosystem.

Yes, major tool providers like IAR and SEGGER have announced support for RISC-V. And because tools like Embedded Workbench and Embedded Studio target the ISA, that’s great news.

But what about something as simple as debug probes, if and when these cores actually make it into silicon?

Software vendors are going to have to hedge their bets when investing in this quickly evolving ecosystem, which will probably end up dictating the initial winners and losers of the RISC-V core wars. Even then, there’s the “custom core” issue mentioned earlier, which in many cases may mean that the core developer or customer will have to patch together specialized software support on their own.

And that too can be extremely expensive. For instance, a recent blog by Rhonda Dirvin, Senior Director of the Automotive and IoT business units at Arm, entitled “The Arm Ecosystem: More than Just an Ecosystem, it’s Oxygen for SoC Design Teams” estimates that software comprises roughly a quarter of SoC development costs.

That, my friends, would be what you call a nonstarter in many cases.

“If you’re in [open source] to make money, you’re in it for the wrong reasons”

This summer I had a chance to visit several vendors in Texas, and met with Geoff Lees, the Senior Vice President and General Manager of Microcontrollers at NXP. He had some very strong opinions on the direction some companies were headed with RISC-V. Most notably, he stated that “If you’re in open source to make money, you’re in it for the wrong reasons.”

Of course, this is easier to say when you’re one of the largest semiconductor manufacturers in the world. NXP and others have the luxury of resources that other smaller companies do not, and they’re positioned in the supply chain such that they can replace small Cortex-M-class cores used for general housekeeping on larger SoCs with RISC-V IP and save on licensing costs.

NXP would also probably like to grow the pie before going all in on a technology like RISC-V. While NXP does have more resources, it also has more to lose.

In the world of open-source software, early pioneers like Red Hat were able to capitalize on Linux by being one of the first to market, but Red Hat was more the exception than the rule. Hell, Linux itself is more the exception than the rule. It's a capitalist world, after all.

So is RISC-V too open to succeed commercially? Maybe. At least for now.