Imperas, Valtrix partner for RISC-V Processor Verification

December 03, 2018

Press Release

Imperas riscvOVPsim virtual platform simulation technology combines with Valtrix verification technology for RISC-V processor test and compliance.

SANTA CLARA, CA — Imperas Software and Valtrix Systems are collaborating on advanced RISC-V Processor test and validation solutions using Valtrix STING SoC design verification tool and Imperas riscvOVPsim RISC-V instruction set simulation (ISS). The collaboration will allow Valtrix to configure virtual platforms as a verification reference and extend the RISC-V envelope model with custom instructions.

The STING software stack is designed as a design verification platform for IP/SoC implementations, and includes a test suite and programming frameworks for custom test development. Tests are compiled with a bare metal microkernel and libraries into a portable program that meets the needs of the verification environment. This program can run in simulated environments such as riscvOVPsim, FPGA prototypes, emulation, or silicon, and execute different test workloads.

“Test and verification of RISC-V open ISA cores is the most demanding challenge for processor developers today,” says Shubhodeep Roy Choudhury, Managing Director & Co-founder, Valtrix. ”By partnering with Imperas and using the OVP virtual library of platforms we can offer customers a complete solution across all aspects of RISC-V processor verification, test and compliance.”

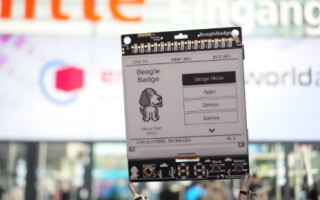

Imperas and Valtrix will be exhibiting at the RISC-V Summit, December 3-6 2018, Santa Clara, California, USA. More details and registration discount codes are available at Imperas.com.