Tear Down: Google Pixel Watch 4

February 03, 2026

Story

When you tear down a smartwatch, you’re rarely surprised by what’s inside.

The surprise usually comes from how the silicon is utilized. That’s certainly the case with Google’s Pixel Watch 4. At first glance, this looks like another high-end Wear OS design built around a Snapdragon application processor. Dig a little deeper, though, and you find that much of the real work, the always-on, battery-sensitive work that defines the user experience, has been quietly offloaded to a highly power-efficient coprocessor. This big-little architecture has become quite popular in high-end wearables.

Two processors, two very different jobs

At the top of the hierarchy is the Snapdragon application processor; no surprise there. It runs Wear OS, drives the UI, handles graphics-intensive effects, and supports Google’s application ecosystem. When you swipe the screen, launch an app, or interact with the display, this processor is up to the task(s).

The Pixel Watch 4 also incorporates an ultra-low-power MCU-class coprocessor from ambiq, from the company’s Apollo5 family. In this case, it was likely the Apollo510. The device is responsible for a large (and growing) share of the watch’s continuous workload, operations that need to be always on.

That includes heart-rate monitoring, motion and activity tracking, sensor fusion, and increasingly, machine-learning-based health and fitness algorithms. These are functions that would shrink the run time if they ran on a high-performance application processor 24/7.

Why the Coprocessor Matters

Battery life is at or near the top of the priority list of smart watches. Consumers want thinner devices, smaller batteries, brighter displays, and more features, and they want them to last more than a day on a charge. You don’t get there by tweaking software alone. You get there by moving the right workloads onto the right silicon.

The ambiq coprocessor is optimized for this role. Its power profile is orders of magnitude lower than that of an application processor, and significantly better than traditional MCUs. That efficiency allows the Pixel Watch 4 to keep sensors running continuously and algorithms processing data in real time without waking up the main processor.

In practice, the coprocessor consumes raw sensor data locally, performs the algorithmic heavy lifting, and passes only higher-level metadata to the Snapdragon processor when needed. That approach reduces both compute load and data movement—two major contributors to power consumption.

AI on the Wrist, Quietly

There’s a tendency to associate AI exclusively with big processors and neural accelerators. In wearables, that’s misleading. Much of what we now label as AI, including sensor fusion, activity classification, gait analysis, ECG, and PPG processing, has been running on ultra-low-power MCUs for quite some time.

In the Pixel Watch 4, those workloads are well-suited to the ambiq coprocessor. Thanks to its efficiency, developers can run far more machine-learning inference than would otherwise be practical. That opens the door to more sophisticated health and fitness features without sacrificing battery life.

The Big-Little Architecture

In a big-little wearable architecture, one of the key questions is whether functions are cleanly partitioned or dynamically shared between processors. The answer, in this case, is both. Some workloads are effectively owned by the coprocessor. Heart-rate tracking and motion sensing, for example, can run autonomously for long periods. Others require coordination. Display updates are a good example. Depending on system state, either processor may be responsible for driving the display, with handoff mechanisms in place to balance responsiveness and power consumption.

This level of coordination requires careful system design. Data moves back and forth, application state changes, and algorithms must adapt as the user switches modes, for example, from idle to a workout session.

Separation Is Key

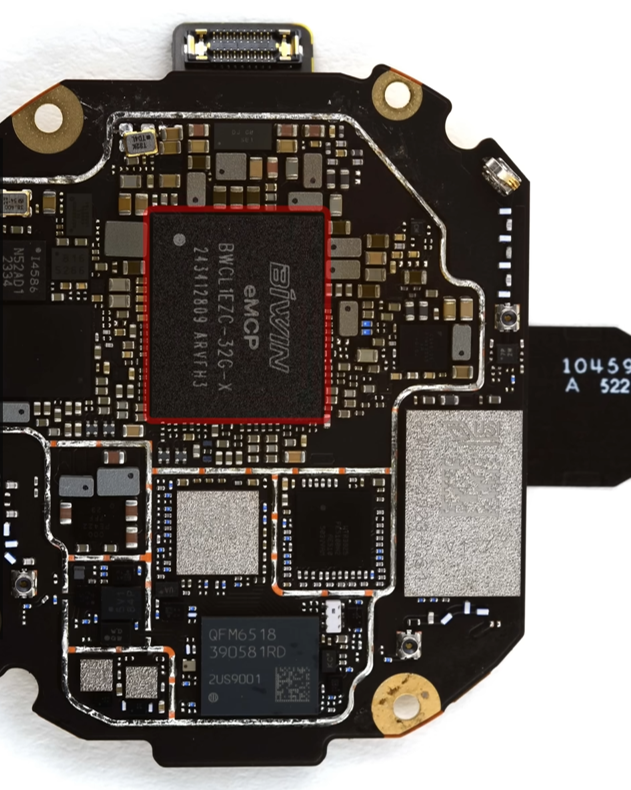

Each processor in the Pixel Watch 4 has its own memory subsystem. The Snapdragon processor is paired with substantial DRAM and mass storage to support Wear OS and applications. The coprocessor relies more heavily on on-chip memory, with optional external RAM or flash as needed.

Each processor also runs its own operating system. The application processor runs the Wear OS, while the coprocessor runs a real-time OS, likely derived from FreeRTOS or a similar RTOS. This separation reinforces the architectural boundary: high-level user experience on one side, deterministic, always-on processing on the other.

ambiq Only

It should be noted that it is possible to design such a device with just the ambiq MCU handling all the functions. As Dan Cermak, ambiq’s Vice President of Architecture and Product Planning, points out, “From a purely technical perspective, it’s definitely possible, and we have customers doing just that. They routinely deliver multi-week battery life.”

The biggest reason Google did not go that route has to do with its ecosystem. Says Cermak, “Wear OS brings an application marketplace, developer tools, and tight integration with Android phones. Replicating that experience on an MCU-based platform would require a massive software investment and significant compromises.”

Google has clearly decided that the benefits of staying within the Wear OS ecosystem outweigh the battery-life gains of an MCU-only design. That’s a reasonable trade-off, but it also explains why Pixel Watch battery life remains measured in days rather than weeks.

Possibilities For a Next Gen

It should be obvious that future improvements could/should come from moving more of the compute functions onto the coprocessor. Every algorithm that can be offloaded extends battery life. And that potentially enables new usage models, like continuous sleep tracking, long-duration health monitoring, and richer AI-driven insights that assume the device is worn 24/7. Those experiences are difficult to deliver when the watch needs to come off the wrist every day for charging.

Such a challenge lies in software optimization, algorithm partitioning, and system-level coordination. This is where ambiq is increasingly collaborating with OEMs, not just supplying silicon, but helping optimize placement, power modeling, and overall efficiency.