MIPI I3C: The Next Generation Serial Bus for System Management

November 17, 2025

Blog

Behind the scenes in a modern PC or server lies a critical sideband communication channel—the System Management Bus (SMBus)—keeping major system components such as the CPU, memory, batteries and power supply running smoothly. It monitors temperature, voltage and current, and controls power delivery across the system, helping each component operate at peak efficiency.

As system components grow in speed and complexity—for example with the advent of JEDEC DDR5 memory modules—the demands on the SMBus have outgrown its original design.

A more advanced communication interface, MIPI I3C® (and its publicly available counterpart MIPI I3C BasicTM), has been gaining traction as an ideal transport choice for system management. This article delves into DDR5 memory modules and examines how the use of I3C can overcome the limitations of legacy SMBus architectures.

DDR5 Memory Modules Require Advanced System Management

In July 2024, JEDEC published its DDR5 SDRAM specification designed to meet demand for increased performance and efficiency.

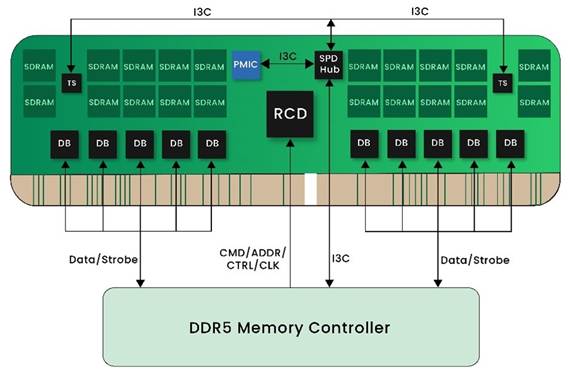

Figure 1. JEDEC DDR5 memory module (Source: Prodigy Technovations)

DDR5 memory modules support higher read/write bandwidth (up to 8.4 GT/s and beyond) and memory capacities up to 64Gb/module. The number of modules that can be supported on a motherboard increased to eight, and operating voltage was lowered from 1.2V to 1.1V—a 20% power reduction compared with previous generations of memory.

Each DDR5 module operates as two independent memory areas, each with a 32-bit subchannel, improving efficiency with multicore CPUs. To support this mode of operation, DDR5 integrates two temperature sensors per module, doubling the number of sensors compared to DDR4. In large systems supporting the maximum eight memory modules, this can result in as many as 16 sensors, all requiring SMBus connectivity.

Another significant development is that DDR5 modules incorporate their own power management ICs (PMICs), generating required voltages directly on the module from a 12V (or 5V for PCs) supply. This effectively makes each module part of the motherboard’s power delivery network and requires every PMIC to be monitored by the SMBus.

Despite their many advantages, compared with previous generations of memory modules, DDR5 modules require three times as many sensors to be connected to the SMBus.

Limitations of Legacy SMBus Architectures

When the SMBus was introduced in 1995, it used the I2C interface as its transport layer. At the time, I2C was well-suited for simple tasks such as temperature or voltage readings and event alerts in systems with relatively few endpoints. As systems have grown more complex—especially with the advent of DDR5 memory, which requires the connection of many more devices—fundamental limitations of the I2C-based SMBus have become clear.

Figure 2. Use of multiplexers in SMBus architectures (Source: MIPI Alliance)

One major challenge is bus loading: The higher number of connected devices increases capacitance, forcing the use of multiplexers (MUXes) between the baseboard management controller (BMC) and SMBus endpoints.

This architecture introduces complications for higher-level system management protocols like DMTF’s Management Component Transport Protocol (MCTP) and Security Protocols and Data Models (SPDM), which rely on query-response transactions. When using these protocols, the BMC must wait for each query-response transaction to be fully completed, tying up the bus and preventing other devices from communicating. For example, an SPDM cryptographic transaction can take up to 100 ms to complete, an unacceptable delay in large data centers with thousands of devices, where MUX switching creates a significant risk of communication glitches and failures.

Figure 3. Example of communication error due to MUX glitches (Source: MIPI Alliance)

MIPI I3C Overcomes Legacy SMBus Limitations

The I2C-based SMBus architecture has additional shortcomings when used for the DDR5 specification:

- Limited speed: I2C’s 1 Mbps maximum bandwidth quickly becomes a bottleneck as the number of sensors and devices grows.

- No interrupt mechanism: Devices must be polled continuously, leading to slower response times and higher power consumption.

- Fixed addressing: I2C uses hardware-strapped addresses. With many identical devices on mass-produced modules, this requires manual remapping to avoid address collisions, increasing system complexity and forcing vendors to maintain large address databases.

To overcome these challenges, in July 2020 JEDEC published its DRAM Module Sideband Bus specification, JESD403-1, built on the MIPI I3C Basic interface. MIPI I3C is an evolutionary interface that improves upon the legacy I2C. It maintains I2C’s two physical pins (SDA and SCL), supports low-power and 11.1 Mbps communication speeds in standard mode, and adds numerous functional improvements.

Use of I3C Basic as a transport for DDR5 system management solves the legacy challenges through:

- In-band interrupts (IBIs): Devices can signal the controller directly using in-band interrupts, avoiding the need to continuously poll devices, which prevents query-response failures. A response may be sent via an interrupt or flagged through a pending-read notification in a GETSTATUS report—ensuring responses are never lost.

- Improved reliability: I3C’s significantly higher transmission speeds reduce the likelihood of communication conflicts, and built-in error recovery further minimizes communication errors such as MUX glitches.

- Dynamic address assignment: I3C eliminates problems caused by using fixed, hardware-strapped addresses, simplifying the deployment of a large number of identical devices.

Additional features include support for 1.0 V to 3.3 V operating voltage, high data rate (HDR) modes up to 33.3 Mbps, hot-join support to allow devices to connect dynamically, target reset using only the SDA/SCL lines, and backward compatibility with legacy I2C devices.

Conclusion

The adoption of a MIPI I3C-based SMBus for JEDEC DDR5 memory resolves many of the limitations of the aging I2C-based SMBus. It delivers faster response times, greater communication reliability and improved scalability—capabilities essential for the next generation of PC and server architectures.

Beyond SMBus, I3C also plays a key role in simplifying sensor integration across smartphones, wearables and IoT devices, and is expanding into more advanced application areas.

Learn more about MIPI I3C and MIPI I3C Basic on the MIPI website, where you can download MIPI I3C Basic, access application notes, a conformance test suite and other useful resources such as white papers, webinars and conference presentations.