Rambus SOCAMM2 Delivers Low-Power LPDDR5X Memory Performance for AI Server Infrastructure

April 23, 2026

News

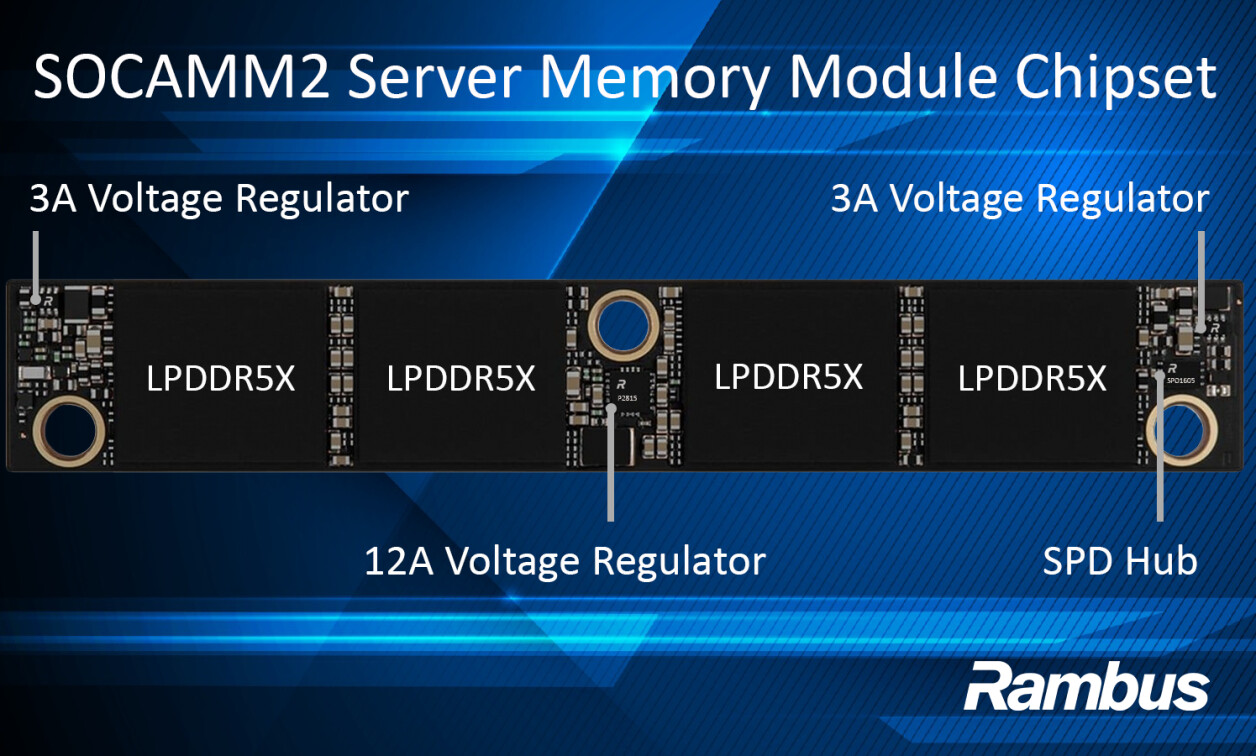

Rambus introduced a SOCAMM2 (Small Outline Compression Attached Memory Module) chipset engineered for low-power, high-performance LPDDR5X-based memory modules for AI servers. The new SKUs enhance Rambus’s offering of complete memory interface chipsets for all JEDEC-standard DDR5 and LPDDR5 memory modules.

“AI system architectures are evolving rapidly, and memory has become one of the most critical enablers of performance, efficiency, and scalability,” said Rami Sethi, SVP and general manager of Memory Interface Chips at Rambus. “SOCAMM2 represents an important step in bringing modular, low-power, high-performance memory into next-generation AI servers. This chipset is the first in a planned family of LPDDR-based server module chips, and we are actively developing the next-generation solutions to enable future AI infrastructure.”

The Rambus SOCAMM2 chipset provides the critical control, telemetry, and power delivery functions required by JEDEC-standard SOCAMM2 memory modules in demanding AI server environments.

According to the press release, the Rambus chipset offers consistent, power-efficient operation of LPDDR-based server memory modules up to 9.6 Gb/s and includes SPD Hub for module identification, configuration, and telemetry and 12-amp (A) and 3A voltage regulators for localized, efficient power conversion.

For more information, visit rambus.com/memory-interface-chips/socamm2-server-chipset/.