New Standardized Interface Targets Key Challenges in Embedded Audio Design

February 04, 2026

Blog

Embedded audio systems increasingly require more sophisticated audio capabilities, both in smaller, denser, feature-rich devices where EMI, power, and space are critical constraints, and in large devices where audio data streams must be reliably transmitted over multi-meter wire lengths.

Consumer electronics devices such as smartphones and earbuds now contain multiple microphones and speakers millimeters away from antennas; automotive architectures require a multitude of audio peripherals connected over long cables that are subject to harsh electromagnetic interference (EMI); and many innovative electronic products are increasingly reliant on the provision of spatial audio, far-field voice recognition, and AI-enhanced signal processing.

MIPI Alliance’s newest audio specification, MIPI SoundWire® I3S v1.0 (MIPI SWI3S™, pronounced “Swiss”), released in October 2025, is a two-pin, multi-drop, half-duplex interconnect designed to transport both audio data and control information with exceptional efficiency, scalability, and robustness. MIPI SWI3S provides higher bandwidth, longer reach, lower EMI, and richer synchronization and command structure than preexisting audio interconnects. For developers working in mobile, automotive, IoT, and industrial domains, SWI3S anticipates the needs of embedded audio requirements for years to come.

Challenges of Legacy Audio Interfaces

Implementing new audio capabilities using traditional audio interconnect technologies such as I2S or TDM has become extremely challenging, as they were never designed to handle the design challenges present within modern audio subsystems. For example, I2S and TDM require multiple signals for data and clocks, which increases pin count and complicates PCB routing in space-constrained designs. Their single-ended signaling makes them vulnerable to EMI, restricts their physical reach, and makes them difficult to use in electrically noisy environments. These interconnects also lack built-in mechanisms for unified control, data transport, or synchronization across multiple devices.

The MIPI SoundWire specification, released in 2015, addressed many of these challenges but was never intended to support multi-meter interface lengths, extremely low EMI emissions, or deeply-tiered device topologies. The new MIPI SWI3S specification is specifically designed to address these challenges and expand the capabilities of MIPI’s audio interface portfolio to meet the requirements of a broad range of system designs — from ultra-compact earbuds and wearables to large, distributed audio systems in PCs, industrial equipment, and automotive platforms.

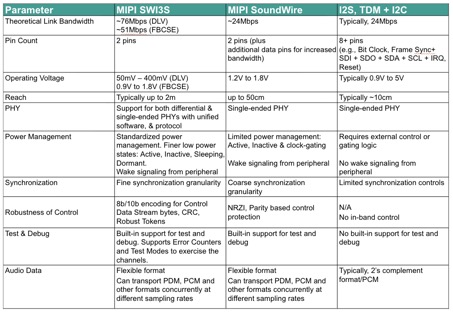

MIPI SWI3S offers higher bandwidth than SoundWire and significantly more than typical I2S and TDM implementations. With its two-pin design, SWI3S keeps pin count low, even as systems scale to include many peripherals. Its longer reach—particularly with its differential low voltage (DLV) PHY—surpasses SoundWire and goes far beyond traditional I2S and TDM interconnects. SWI3S implements standardized power states and wake signaling, whereas legacy interfaces typically rely on external control logic. Additionally, SWI3S integrates robust in-band control transport and synchronization, which is not supported by I2S or TDM.

The accompanying table provides a comparison between MIPI SWI3S, MIPI SoundWire, and the legacy interfaces I2S and TDM with I2C.

Table: Comparison of MIPI SWI3S and MIPI SoundWire with legacy interfaces

Inside MIPI SWI3S: Architecture and Operation

MIPI SWI3S introduces several innovations in how audio data and control commands are transported over a two-wire interface.

At its core, SWI3S defines a unified two-wire interconnect in which a manager (typically an SoC) communicates with up to 12 audio peripherals, such as microphones, amplifiers, or codecs. All audio payloads, synchronization events, and control commands share this single half-duplex, two-wire connection.

A key design feature of SWI3S is its row-and-column bitstream structure, which deterministically allocates bandwidth among audio streams, control transactions, and timing markers. This structure allows peripherals to generate precisely-timed sampling events aligned with the manager’s clock—critical for enabling spatial audio processing, beamforming, and multi-microphone synchronization.

MIPI SWI3S also integrates a robust command and control channel based on 8b/10b encoding, which enhances error detection, improves EMI characteristics, and ensures robust in-band command transport. Commands follow structured request and response phases, and the protocol incorporates commit timing to ensure synchronized updates across multiple peripherals.

The need for power efficiency receives significant attention in SWI3S. The interconnect introduces a rich set of link states—active, inactive, sleeping, along with a peripheral dormant state—giving system developers fine-grained control over power consumption. Peripherals can independently trigger wake events, and all control signaling remains in-band.

Physical Layer (PHY) Options and Performance

SWI3S supports two physical layers: a differential low voltage (DLV) PHY designed for very low EMI and long reach, often up to two meters, while delivering high bandwidth approaching 76 Mbps; and a forwarded bit-clock single-ended (FBCSE) PHY optimized for short-range, low-power, and cost-sensitive devices. The two PHYs share a unified protocol and software layer, allowing systems to mix and match signaling methods across the same overall audio network. This flexibility is particularly useful when balancing cost, EMI, and routing constraints.

Flexible Topologies and System Integration

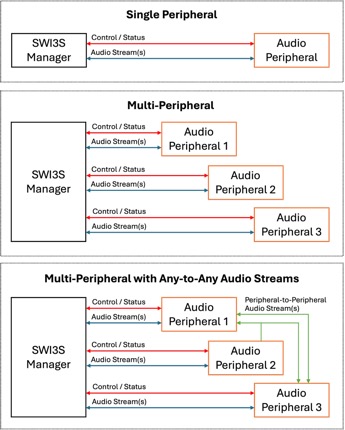

The new MIPI SWI3S specification supports flexible multi-drop architectures that can include multiple branches or device clusters. These topologies maintain deterministic synchronization and predictable scheduling across all devices thanks to the structured bitstream. The figure below illustrates possible SWI3S network topologies, demonstrating support for branched, multi-device audio networks with consistent synchronization across all endpoints.

Figure: Example SWI3S network topologies

Future MIPI SWI3S Enhancements

Upcoming enhancements to the SWI3S specification will enable audio peripherals to act as hubs, supporting tiered mixed-PHY network designs that combine long-reach DLV backbones with simpler local PHYs at the edge. Such designs can reduce loading, improve timing, and enable zonal power management with independent data rates. Hubs will also support local device-to-device communication and distributed processing. In addition, the next release of SWI3S will run over existing SoundWire PHYs, allowing developers to reuse current silicon and migrate their designs more easily to the new protocol.

Resources for Embedded Audio System Developers

For more information about SWI3S, download the technical brief “An Introduction to the MIPI SWI3S Audio Interface.” MIPI also recently presented an Audio Webinar Series, which featured three webinars covering the entire MIPI audio portfolio, related software specifications and tools, and a detailed look at the new SWI3S specification. All webinars are available to watch on demand. To learn more about companies leveraging SWI3S in their product portfolios, visit the MIPI SWI3S Ecosystem page.

As embedded audio systems become more intelligent and acoustically demanding, engineers require an interface that provides high bandwidth, long reach, precise synchronization, low EMI, and power efficiency—all without increasing pin count or firmware complexity. MIPI SWI3S delivers on all these requirements, offering a unified two-wire solution suitable for microphones, amplifiers, codecs, sensor arrays, and distributed audio processing nodes.

With its scalable protocol, flexible PHY options, and upcoming support for hub-based topologies and SoundWire PHY operation, SWI3S is poised to become a foundational audio interconnect for the next generation of embedded systems.