Achieving Your Low Power Goals with Synopsys Ultra Low Leakage IO

May 12, 2023

Whitepaper

The demand for low power design has intensified with shrinking geometries.

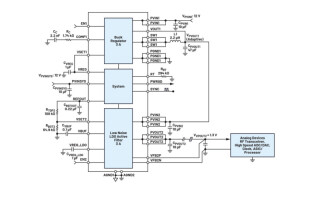

At the same time, innovation in battery operated, handheld devices has increased the design complexity by adding more and more functionality. The focus is on power-optimized designs, one of the most critical requirements in consumer and mobile applications, while maintaining low cost and reduced risk. General Purpose IOs (GPIOs) are essential blocks for system-on-chips (SoCs). GPIOs are the standard chip interfaces that communicate between on-chip logic operating at low voltages, and off-chip components operating at similar or higher voltages. As functionality is added to the SoC, the number of pin connections to the external interfaces increases, and therefore the number of GPIOs needed in the SoC increases. With so many GPIOs in a design, it is critical to ensure they consume as little leakage power as possible to minimize the impact on the overall leakage at the SoC level while maintaining high frequencies of 100s of MHz for proper IO operation.

At the same time, innovation in battery operated, handheld devices has increased the design complexity by adding more and more functionality. The focus is on power-optimized designs, one of the most critical requirements in consumer and mobile applications, while maintaining low cost and reduced risk. General Purpose IOs (GPIOs) are essential blocks for system-on-chips (SoCs). GPIOs are the standard chip interfaces that communicate between on-chip logic operating at low voltages, and off-chip components operating at similar or higher voltages. As functionality is added to the SoC, the number of pin connections to the external interfaces increases, and therefore the number of GPIOs needed in the SoC increases. With so many GPIOs in a design, it is critical to ensure they consume as little leakage power as possible to minimize the impact on the overall leakage at the SoC level while maintaining high frequencies of 100s of MHz for proper IO operation.

This whitepaper explains the need for ultra low leakge (ULL) GPIOs, the optimization techniques used to reduce leakage, and the inherent tradeoffs to consider. In addition, it describes how Synopsys ULL GPIOs help designers reduce leakage while achieving the SoC power and performance targets for mobile and battery-driven devices used in AI and sensing applications.

Download WhitepaperDownload Whitepaper