Upbeat and SiFive to Demonstrate Dual-Core RISC-V Microcontrollers with AI Acceleration at RISC-V Summit

October 20, 2025

News

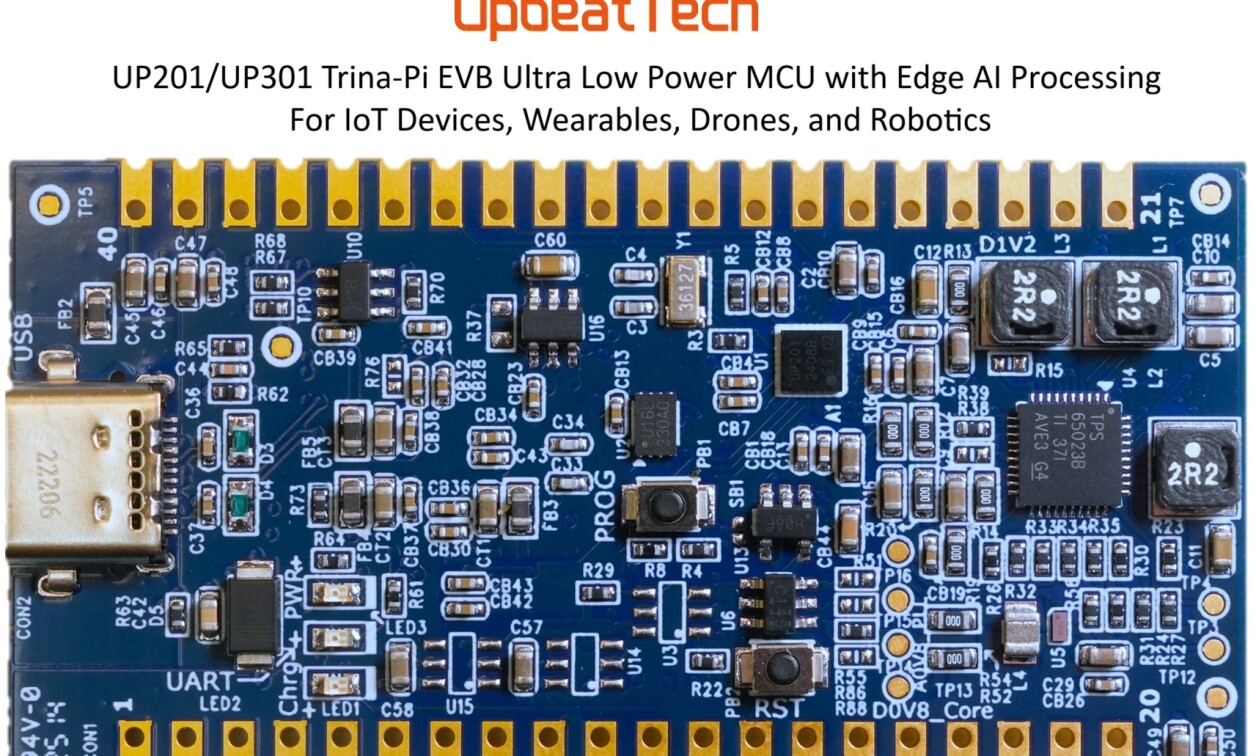

Upbeat Technology and SiFive, Inc. introduced the UP201/UP301 family MCU, a dual-core RISC-V microcontroller engineered for ultra-low power efficacy. The companies plan to exhibit the solutions at the upcoming RISC-V Summit in Santa Clara, California from October 22–23, 2025.

The UP201/UP301 MCUs integrates two SiFive Essential IP Cores and two AI accelerators designed by Upbeat, enabling market-leading performance per watt while supporting always-on IoT devices, wearables, drones, and edge AI inference.

Due to its combination of near‑threshold operation, Error Detection and Correction (EDAC) resilience, and SRAM innovation, the MCUs deliver energy efficiency at 16.8 uW/MHz/DMIPS (Dhrystone).

When juxtaposed with general ARM‑based microcontroller architectures, the MCU portfolio enhances design with a scalable (up to 400 MHz or 717 DMIPS) production‑ready platform that balances performance, efficiency, and intelligence for next‑generation connected devices.

“From bring-up to production, Upbeat Technology’s UP201/UP301 family of MCUs has been very easy to work with. Its power profiles exceeded our targets—ultra-low power in sleep and highly efficient under active load. The integrated AI accelerator and DSP offload inference and signal processing, enabling us to meet real-time deadlines. Thanks to the SoC’s low-power, high-performance architecture, we can push more on-device processing—richer models, longer duty cycles, and new features—without compromising battery life,” said FuJen Hsiao, CEO, Awan-sensing.

Visitors will also be able to see Upbeat Technology’s ‘A Heterogeneous Dual-Core RISC-V Edge AI Platform for Power-Efficient Machine Learning’ on October 22, 2025, at 11:10 a.m., featuring live demos and hands-on training with the UP201/UP301 family MCU.

For more information, visit sifive.com and upbeattechtw.com.